El transceptor óptico 100G FR1 SFP56-DD FR1 está diseñado para su uso en enlaces Ethernet de 100 Gigabits de hasta 2 km sobre fibra monomodo (SMF). Es compatible con SFP56-DD MSA, IEEE802.3CU, 100G Lambda 100G FR1 y 100GAUI-2 (sin FEC)¹. Las funciones de diagnóstico digital están disponibles a través de la interfaz I²C, según lo especificado por SFP56-DD MSA.

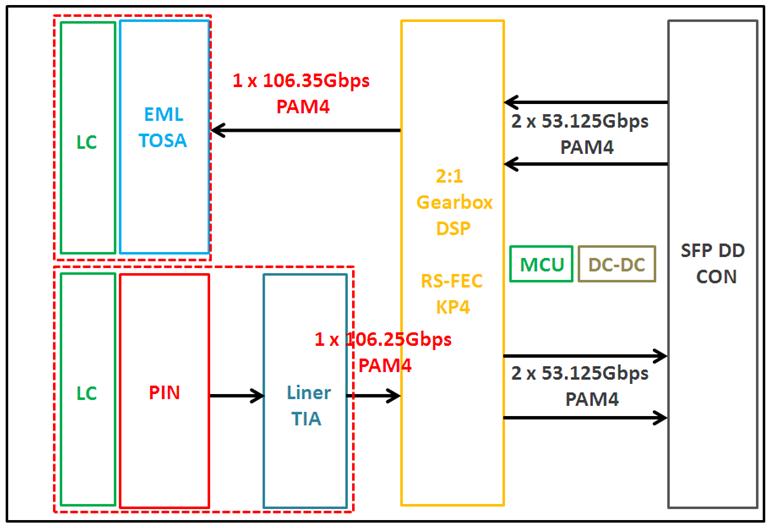

El módulo incorpora una señal óptica de un canal con una longitud de onda central de 1311 nm y opera a una velocidad de datos de 100 Gbps. Este módulo puede convertir dos canales de datos de entrada eléctrica de 53 Gbps (PAM4) en un canal de señal óptica de 106 Gbps (PAM4), y también puede convertir un canal de señal óptica de 106 Gbps (PAM4) en dos canales de datos de salida eléctrica de 53 Gbps (PAM). La interfaz óptica utiliza un conector LC dúplex. El transmisor EML refrigerado de alto rendimiento y el receptor PIN de alta sensibilidad ofrecen un rendimiento superior para aplicaciones Ethernet de 100 Gigabits con enlaces de hasta 2 km.

Transceptor óptico SFP-DD 100G FR1 de 2 km RSD-100G-FR1

Características

Aplicaciones

Nota:

1. KR-FEC es opcional, contáctenos si es necesario.

Figura 1. Diagrama de bloques del módulo

Calificaciones máximas absolutas

| Parámetro | Símbolo | Mínimo | Máximo | Unidad |

| Voltaje de suministro | Vcc | -0.3 | 3.6 | V |

| Voltaje de entrada | Vin | -0.3 | Vcc+0,3 | V |

| Temperatura de almacenamiento | Ts | -20 | 85 | ºC |

| Temperatura de funcionamiento de la caja | Tc | 0 | 70 | ºC |

| Humedad (sin condensación) | Rh | 5 | 85 | % |

Condiciones de funcionamiento recomendadas

| Parámetro | Símbolo | Mínimo | Típico | Máximo | Unidad |

| Voltaje de suministro | Vcc | 3.13 | 3.3 | 3.47 | V |

| Temperatura de funcionamiento de la caja | Tc | 0 | 70 | °C | |

| Velocidad de datos por carril | fd | 106.25 | Gb/s | ||

| Humedad | Rh | 5 | 85 | % | |

| Disipación de potencia | P.m | 3 | 3.5 | O | |

| Distancia de enlace con G.652 | D | 2 | kilómetros |

Especificaciones eléctricas

| Parámetro | Símbolo | Mínimo | Típico | Máximo | Unidad |

| Impedancia de entrada diferencial | Zin | 90 | 100 | 110 | ohm |

| Impedancia de salida diferencial | Zout | 90 | 100 | 110 | ohm |

| Amplitud de voltaje de entrada diferencial1 | ΔVin | 1600 | mVp-p | ||

| Amplitud de voltaje de salida diferencial2 | ΔVsalida | 900 | mVp-p |

Nota:

1. La amplitud del voltaje de entrada diferencial se mide entre TxnP y TxnN.

2. La amplitud del voltaje de salida diferencial se mide entre RxnP y RxnN.

Características ópticas

| Parámetro | Símbolo | Mínimo | Típico | Máximo | Unidad | Notas |

| Transmisor | ||||||

| Longitud de onda central | λc | 1304.5 | 1317.5 | Nuevo Méjico | ||

| Relación de supresión de modo lateral | SMSR | 30 | dB | |||

| Potencia de lanzamiento media | Abadejo | -2.4 | 4 | dB | ||

| Cierre del ojo del transmisor y de dispersión (TDECQ) | TDECQ | 3.4 | dBm | |||

| Tasa de extinción | Sala de emergencias | 3.5 | dB | |||

| Potencia de lanzamiento promedio del transmisor APAGADO | -15 | dB | ||||

| Receptor | ||||||

| Longitud de onda central | λc | 1304.5 | 1317.5 | Nuevo Méjico | ||

| Sensibilidad del receptor en OMA exterior | RXsen | -4.5 | dBm | 1 | ||

| Potencia de recepción media | Alfiler | -6.4 | 4.5 | dBm | ||

| Reflectancia del receptor | -26 | dB | ||||

| LOS Assert | -13 | dBm | ||||

| LOS De-Assert – OMA | -11 | dBm | ||||

| Histéresis LOS | 0.5 | dB | ||||

Nota:

1. Medido con señal de prueba de conformidad en TP3 para BER = 2.4E-4 Pre-FEC

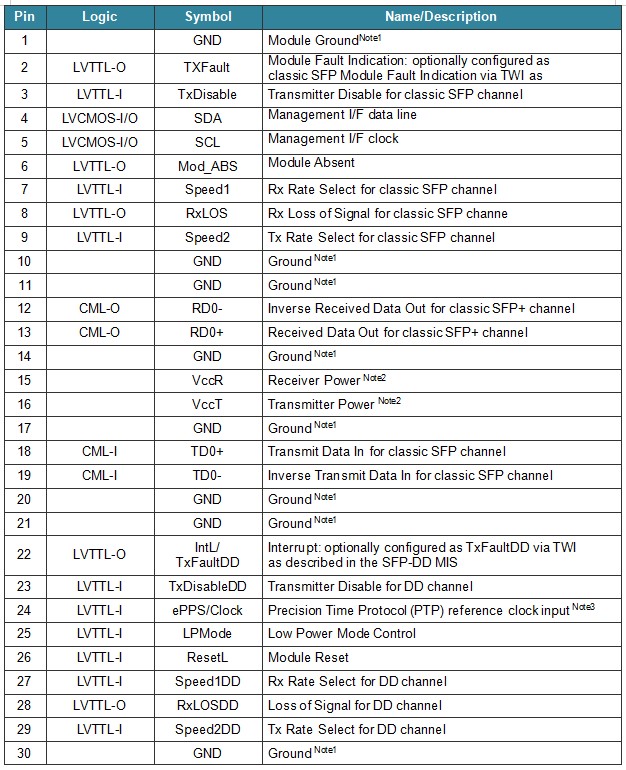

Descripción del pin

Nota:

1. El SFP-DD utiliza una conexión a tierra común (GND) para todas las señales y la alimentación. Todas son comunes dentro del módulo SFP-DD y todos los voltajes del módulo se refieren a este potencial, a menos que se indique lo contrario. Conéctelos directamente al plano de tierra común de la señal de la placa base.

2. VccR y VccT se aplicarán simultáneamente, al igual que VccR1 y VccT1. Requisitos definidos para el host. Los pines Vcc del conector están clasificados para una corriente máxima de 1000 mA.

3. Los pines ePPS (si no se utilizan) pueden terminarse con 50 a tierra en el host.

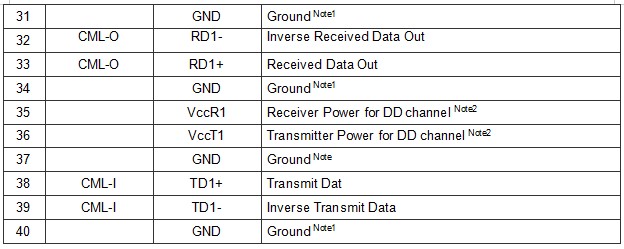

Figura 2. Detalles de la distribución de pines eléctricos

Velocidad1, Velocidad2, Velocidad1DD, Velocidad2DD

Speed1, Speed2, Speed1DD y Speed2DD son entradas del módulo y se conectan a tierra mediante resistencias de >30 kΩ en el módulo. Speed1 selecciona opcionalmente la velocidad de recepción de la señal óptica para el canal 1. Speed1DD selecciona opcionalmente la velocidad de recepción de la señal óptica para el canal 2. Speed2 selecciona opcionalmente la velocidad de transmisión de la señal óptica para el canal 1. Speed2DD selecciona opcionalmente la velocidad de transmisión de la señal óptica para el canal 2.

Nota: A 128 GFC, el FC LSN ya no requiere usar Speed1, Speed2, Speed1DD y Speed2DD; se está considerando recuperar estas señales para funciones programables u otras.ResetL Pin

Reinicio. LPMode_Reset cuenta con una función pull-up interna en el módulo. Un nivel bajo en el pin ResetL durante más tiempo que la duración mínima del pulso (t_Reset_init) inicia un reinicio completo del módulo, restableciendo todos los ajustes del módulo de usuario a su estado predeterminado. El tiempo de confirmación de reinicio del módulo (t_init) comienza en el flanco ascendente tras liberarse el nivel bajo en el pin ResetL. Durante la ejecución de un reinicio (t_init), el host ignorará todos los bits de estado hasta que el módulo indique la finalización de la interrupción de reinicio. El módulo lo indica mediante una señal IntL con el bit Data_Not_Ready negado. Tenga en cuenta que al encenderse (incluida la inserción en caliente), el módulo indicará la finalización de la interrupción de reinicio sin necesidad de reiniciar.

Mod_ABS

El Mod_ABS debe estar conectado a Vcc Host en la placa host y conectado a nivel bajo en el módulo. El Mod_ABS se activa en "Bajo" al insertar el módulo. Se desactiva en "Alto" cuando el módulo no está físicamente conectado al conector host debido a la resistencia pull-up de la placa host.

Modo LP

LPMode es una señal de entrada del host que opera con lógica alta activa. La señal LPMode debe elevarse a Vcc en el módulo SFP-DD/SFP-DD112. Esta señal permite al host definir si el módulo SFP-DD/SFP-DD112 permanecerá en modo de bajo consumo hasta que el software habilite la transición al modo de alto consumo, según lo definido en la especificación de administración de SFP-DD. En modo de bajo consumo (LPMode desactivado en bajo), el módulo puede pasar inmediatamente al modo de alto consumo tras inicializarse la interfaz de administración.

RestablecerL

La señal ResetL se conectará a Vcc en el módulo. Un nivel bajo en la señal ResetL durante un tiempo superior a la duración mínima del pulso (t_Reset_init) inicia un reinicio completo del módulo, restableciendo la configuración predeterminada del módulo.

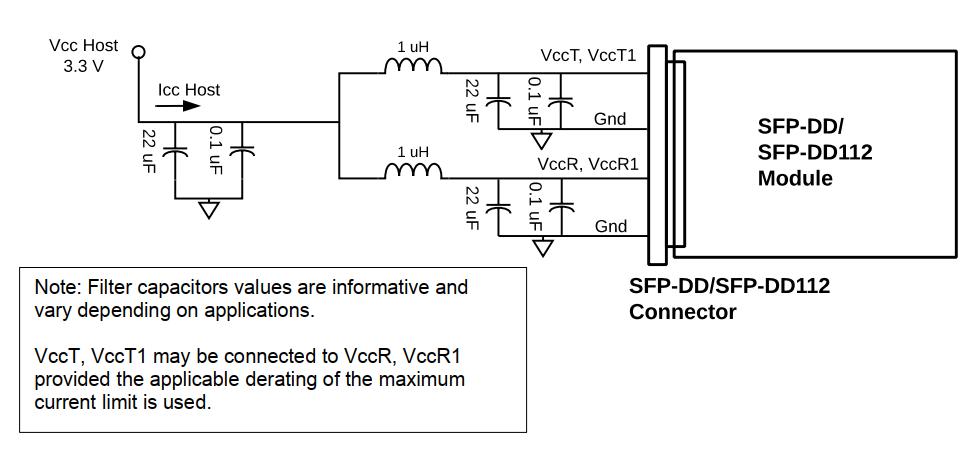

Filtrado de la fuente de alimentación

La placa host debe utilizar el filtrado de fuente de alimentación que se muestra en la Figura 3.

Figura 3. Filtrado de la fuente de alimentación de la placa host

INTERFAZ DE MONITOREO DE DIAGNÓSTICO (OPCIONAL)

Las siguientes características de diagnóstico digital se definen en condiciones normales de funcionamiento, a menos que se especifique lo contrario.

| Parámetro | Símbolo | Mínimo | Máximo | Unidades | Notas |

| Error absoluto del monitor de temperatura | Temperatura DMI | -3 | +3 | grados Celsius | Por encima del rango de temperatura de funcionamiento |

| Error absoluto del monitor de tensión de alimentación | DMI_VCC | -0.1 | 0.1 | V | En todo el rango operativo |

| Error absoluto del monitor de potencia del canal RX | Canal DMI_RX | -2 | 2 | dB | 1 |

| Monitor de corriente de polarización del canal | DMI_Ibias_Ch | -10% | 10% | mamá | |

| Error absoluto del monitor de potencia del canal TX | Canal DMI_TX | -2 | 2 | dB | 1 |

Notas:

1. Debido a la precisión de la medición de diferentes fibras monomodo, podría haber una fluctuación adicional de +/-1 dB o una precisión total de +/- 3 dB.

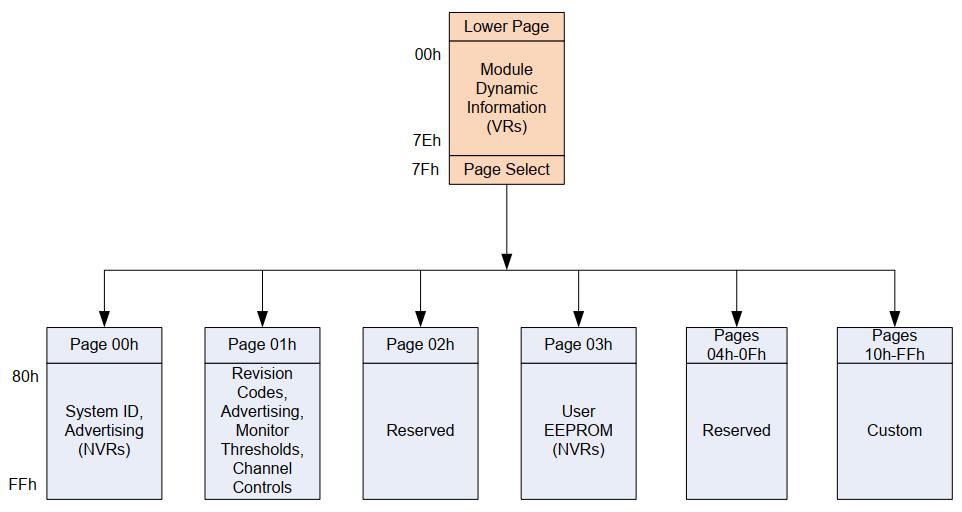

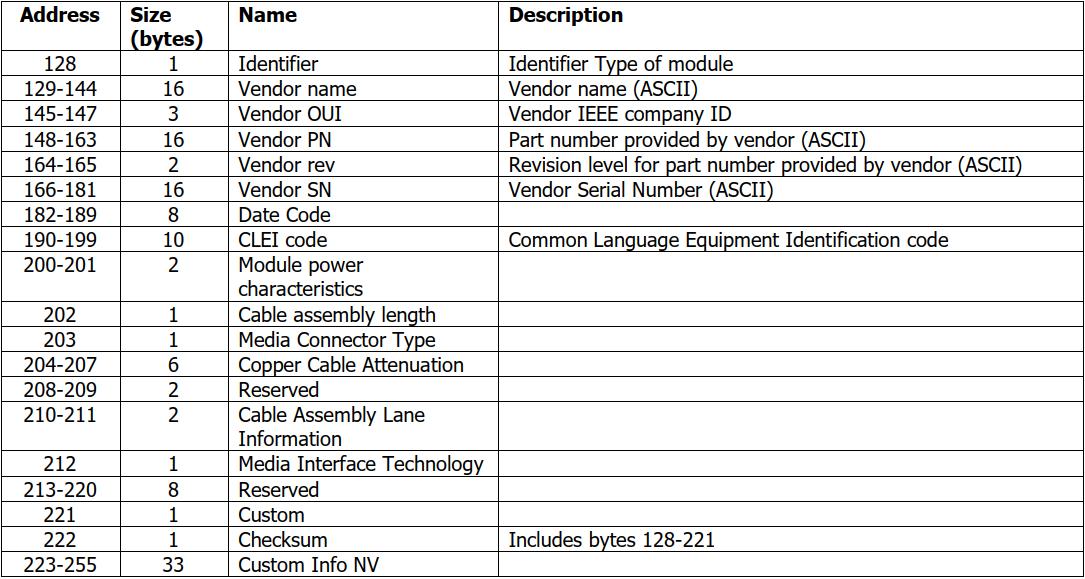

Las funciones de diagnóstico digital están disponibles a través de la interfaz I₂C, según lo especificado por SFP-DD MIS. La memoria de gestión de SFP-DD MIS se muestra en la Figura 4.

Debido a las direcciones de ocho bits, esto limita la memoria de administración a la que el host puede acceder directamente a 256 bytes, que se divide en memoria inferior (direcciones 00h a 7Fh) y memoria superior (direcciones 80h a FFh).

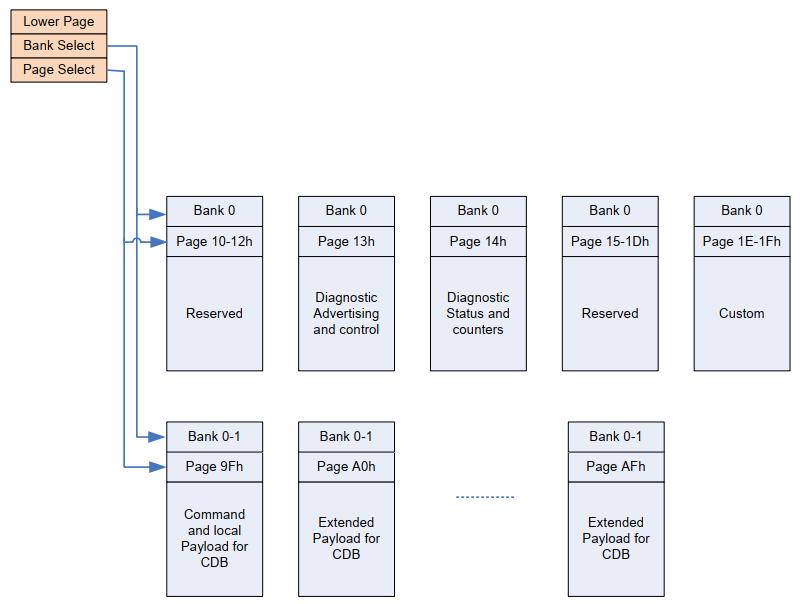

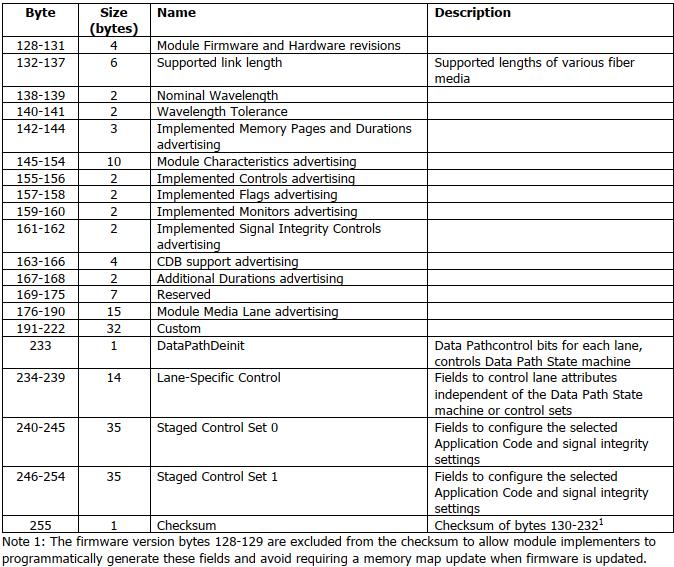

La estructura de direccionamiento de la memoria de gestión interna adicional1 se muestra en la Figura 5.

La memoria de gestión del módulo se organiza como un espacio de direcciones único y siempre accesible para el host de 128 bytes (Memoria Inferior) y como múltiples subespacios de direcciones superiores de 128 bytes cada uno (Páginas), de los cuales solo uno se selecciona como visible para el host en la Memoria Superior. Es posible un segundo nivel de selección de páginas para las que existen varias instancias (por ejemplo, cuando existe un banco de páginas con el mismo número de página).

Esta estructura admite una memoria plana de 256 bytes para módulos pasivos de cobre y permite el acceso oportuno a direcciones en la memoria inferior, como indicadores y monitores. Las entradas menos urgentes, como la información de ID de serie y la configuración de umbrales, están disponibles con la función de selección de página en la página inferior. Para módulos más complejos que requieren mayor memoria de administración, el host debe usar la asignación dinámica de las distintas páginas al espacio de direcciones direccionable de la memoria superior, siempre que sea necesario.

Nota: El mapa de memoria de gestión se diseñó en gran medida basándose en el mapa de memoria CMIS, donde se utilizan páginas y bancos para permitir interacciones críticas entre el host y el módulo, a la vez que se amplía el tamaño de la memoria. Este mapa de memoria se modificó para admitir solo dos carriles eléctricos y limitar la memoria requerida. Se utiliza el enfoque de dirección única, tal como se utiliza en QSFP.

Figura 4. Mapa de memoria QSFP28

Figura 5. Mapa de memoria de la página del banco MIS SFP-DD

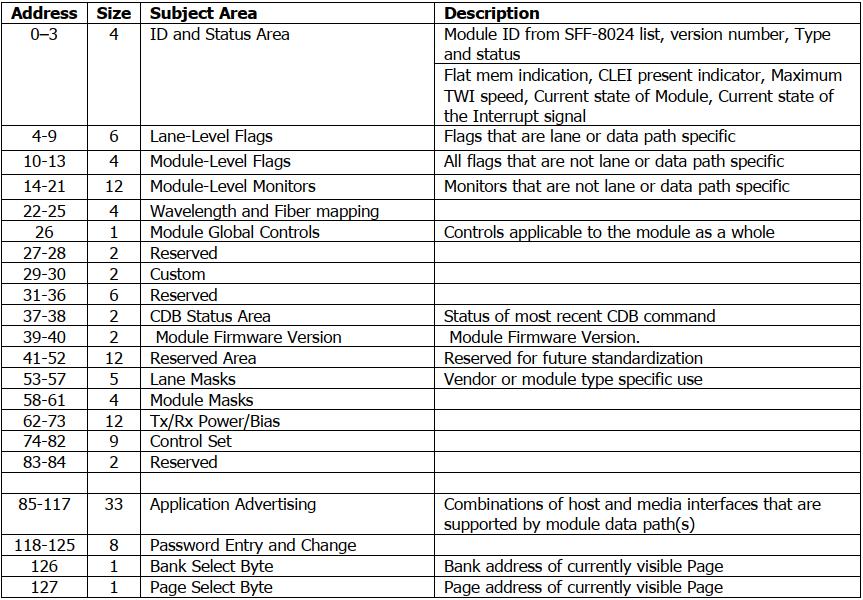

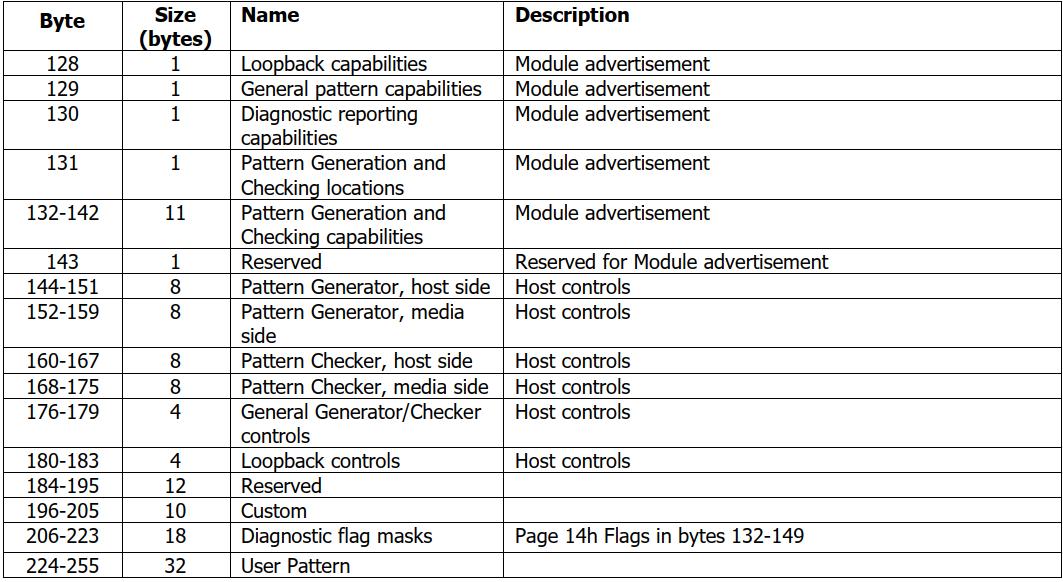

Figura 6. Descripción general de la memoria inferior

Figura 7. Página 00h Descripción general de la memoria

Figura 8. Página 01h Descripción general de la memoria

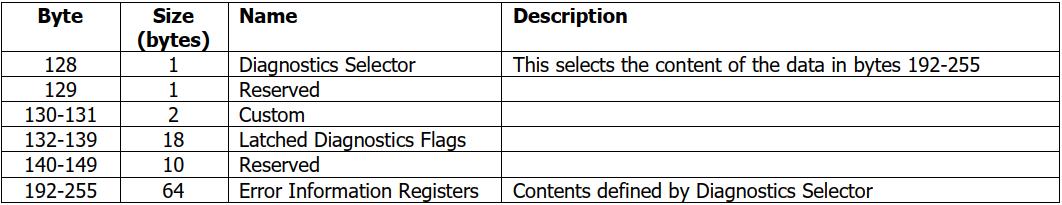

Figura 9. Página 13h Descripción general de la memoria

Figura 10. Página 14h Descripción general de la memoria

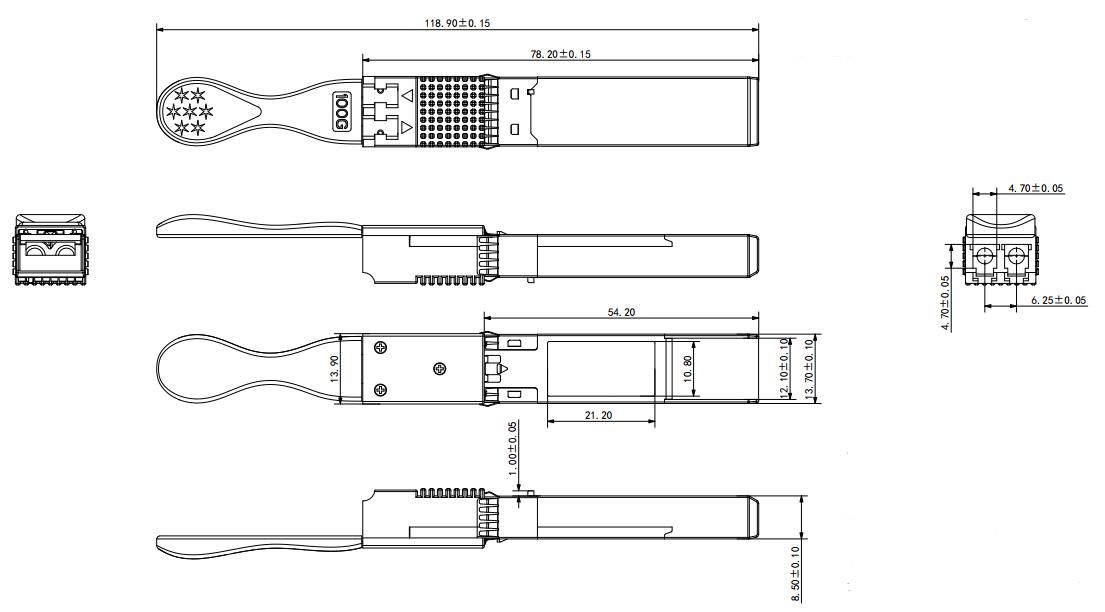

Dimensiones mecánicas

Figura 8. Especificaciones mecánicas

Información de pedidos

| Número de pieza | Descripción del Producto |

| RSD-100G-FR1 | SFP56-DD FR1, 106,25 Gb/s, 2 km, EML+PIN, SMF, LC doble |

¿Quieres saber sobre este producto?

Si Usted está interesado en nuestros productos y desea saber más detalles, deje un mensaje aquí, le responderemos tan pronto como nosotros ... puedamos.